# 2023 IEEE ASSCC Review

KAIST 전기및전자공학부 박사과정 임규완

## **Session 7 Emerging Sensors and Displays**

"Emerging Sensors and Displays" 라는 주제로 만들어진 이번 ASSCC의 7번 session에서는 총 4편의 논문이 reflectometer, display driver, touch sensor, multiple access sensor node 등의 다양한 주제로 발표되었다. 이번 review에서는 이 중 특별히 display driver과 touch sensor에 대한 논문을 살펴보겠다. Display driver은 2010년대 중반까지 활발히 연구되다가 잠시 주요 학회에 논문이 제출되지 않았으나, 최근 몇 년간 ISSCC 및 VLSI 등 학회에 다시 활발히 논문이 제출되는 분야로써, 특히 VR 및 AR과 관련된 display 회로 분야가최근 관심을 받고 있다. Touch sensor은 주요 학회에 논문이 많이 제출되는 분야는 아니지만, 꾸준히 논문이 제출되고 있으며, 특히 최근 ISSCC 23년도에도 touch sensor 논문이출간된 바가 있다.

### # 7-2

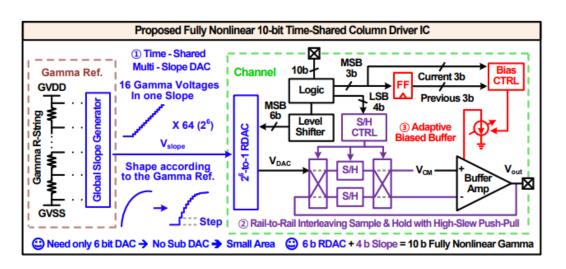

[그림 1] 논문에서 제안하는 time-shared display driver IC 구조

7-1번 논문은 기존의 conventional display driver의 가장 큰 단점인 color depth의 증가에 따른 driver size의 exponential한 증가를 막고, piecewise linear interpolation의 단점인

effective bit 감소 또한 막고자 제시된 구조이다. 제안하는 구조는, 기존의 interpolation과 유사한 방식으로 채널 내에 존재하는 R-DAC, 즉 switch array의 resolution을 줄여 column channel circuit의 size를 크게 감소시키고, R-DAC의 resolution 감소로 인해 사라진 resolution은 interpolation 대신 gamma voltage slope를 이용한 sample & hold 방식으로 생성하여 10-bit voltage를 만들어 낸다.

Gamma voltage slope를 이용한 sample & hold 방식은 다음과 같이 동작한다. 먼저, 10-bit reference gamma 전압을 16개의 전압을 가지는 64개 (6-bit)의 구간으로 나눈 후, 1-H time 동안 각 구간의 16개 전압이 한단계 (=1LSB)씩 올라가면서 출력되는 64개의 voltage slope을 만들어 낸다. 그 후, 각 채널은 MSB 코드를 이용해서 64개의 voltage slope 중 하나를 선택하고, LSB 코드를 이용하여 slope의 전압 중 입력 code에 해당하는 전압을 sample한다. 마지막으로, sample 된 전압은 다음 1-H time에 amp 및 buffer에 연결되어 driving 된다.

위의 동작은 하나의 sampling cap만 이용한다면 sample 하는데 1-H time, driving 하는데 1-H time이 필요하여 총 2개의 1-H time이 필요한데, 제안하는 work에서는 2개의 sampling cap을 사용하여 다른 하나의 cap이 출력을 driving 할 때 나머지 cap이 전압을 sampling 하도록 하여 1-H time동안 입력 data에 대한 전압을 driving 할 수 있도록 하였다.

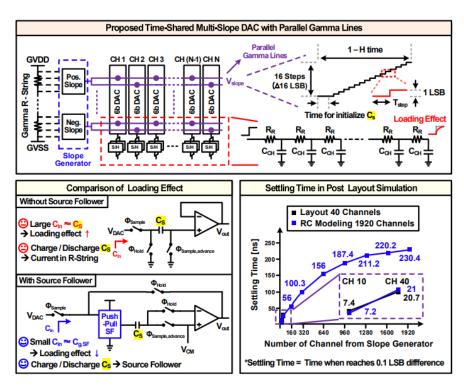

[그림 2] 논문에서 제안한 cap loading effect 감소 구조

하지만, 이러한 형태의 회로에서는 한 가지 문제가 있다. 제안하는 구조는 global reference의 출력 전압을 sampling하는 구조이고, global reference의 R-string 저항 및 routing line의 저항이 sampling cap을 driving 해야 한다. 게다가 display driver은 multichannel 구조이기 때문에, 여러 채널의 sampling cap이 하나의 큰 capacitor로 보이므로 이는 R-string 저항 및 routing 저항과 함께 큰 time-constant를 만들어 각 capacitor의 전압이 settling 하는데 긴 시간이 걸리게 할 수 있다.

따라서, 제안하는 work에서는 그림 2와 같이 각 capacitor의 앞에 source follower을 삽입하여 R-string 및 routing 저항에서 보이는 effective capacitor을 작게 줄여 capacitor의 전압이 settling 하는 데 걸리는 시간을 voltage slope의 하나의 전압이 올라가는 데 걸리는 시간보다 짧게 줄였다.

제안하는 work은 이전 work에 비해 fully nonlinear한 전압을 driving 할 수 있다는 장점이 있고, interpolation을 사용하지 않고도 6+4 interpolation과 비슷한 효과를 내어 channel의 size를 줄였다는 장점이 있다. [표 1]에서 제안하는 work의 장점과 size shrinkage를 볼 수 있다.

|                                                       | JSSC 2009 [1]                         | JSSC 2021 [4]                         | VLSI 2021 [5]                         | ISSCC 2022 [6]                        | This work                             |

|-------------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| Technology                                            | 100 nm                                | 90 nm                                 | 180 nm                                | 130 nm                                | 180 nm                                |

| Color Depth<br>(Nonlinear Bit +<br>Interpolation Bit) | Piecewise Linear<br>10-bit<br>(6 + 4) | Fully Nonlinear<br>10-bit<br>(10 + 0) | Piecewise Linear<br>12-bit<br>(7 + 5) | Piecewise Linear<br>10-bit<br>(8 + 2) | Fully Nonlinear<br>10-bit<br>(10 + 0) |

| Output Range                                          | 0V to 5V                              | 0.2 V to 4.8 V                        | 0.1 V to 4.9 V                        | 0.3 V to 4.5 V                        | 0.2 V to 4.8 V                        |

| INL / DNL [LSB]                                       | 1.71 / 0.37                           | 0.42 / 0.2                            | 0.95 / 0.43                           | 0.9 / 0.39                            | 0.89 / 0.46                           |

| Max. DVO                                              | 6.4 mV                                | 7.9 mV                                | 7.9 mV                                | 4.82 mV                               | 7.47 mV                               |

| Static Current per Ch.                                | 1.2 µA                                | 2.8 μΑ                                | 2 μΑ                                  | 1.8 µA                                | 1.4 μA**                              |

| Silicon Area per Ch.                                  | 6622 μm²<br>(473 x 14)                | 5328 µm²<br>(296 x 18)                | 5015 µm²<br>(295 x 17)                | 2688 µm²<br>(168 x 16)                | 6444 µm²<br>(358 x 18)                |

| Area Shrinkage*                                       | 8.2 %                                 | 31.0 %                                | N/A                                   | 65.2%                                 | 44 %                                  |

| Nonlinear Gamma<br>Voltage Driving                    | х                                     | 0                                     | х                                     | х                                     | 0                                     |

| Interpolation Method                                  | Current DAC                           | Capacitor DAC                         | Capacitor DAC                         | Capacitor DAC                         | Time-Shared Gamma<br>Slope Sampling   |

| Adaptive Biasing                                      | X                                     | X                                     | 0                                     | X                                     | 0                                     |

<sup>\*</sup> Compared to conventional 8b RDAC. Layout was individually done by each reference \*\*Averaged

[표 1] 성능 비교표

마지막으로, 제안하는 work의 단점을 몇 가지 살펴보자면, sampling 방식이 사용됨에도 불구하고 main amplifier의 offset이 sample 될 수 없다는 점과, main amplifier의 offset이 main amp의 input capacitor과 sampling capacitor의 비율로 증폭이 된다는 단점이 있다. 이에 관하여 한 가지 이상한 점은, fig. 4에는 main amplifier의 offset을 sample하여 이를 cancel하는 것처럼 설명되어 있다는 점인데, 제안하는 DAC의 동작 상 main amplifier은 sampling 과정에 참여할 수 없으므로 main amp의 offset은 cancel될 수 없다.

또한, 1-H time 동안 16단계의 전압이 각 capacitor의 전압에 settling 되면서 올라가야 하므로 1-H time이 더 짧아지는 application에서는 더 많은 전류를 소모하거나, 전압 단계를 줄여서 speed를 올리고 driver size를 증가시켜야 할 수 있다는 단점이 있다.

#### # 7-3

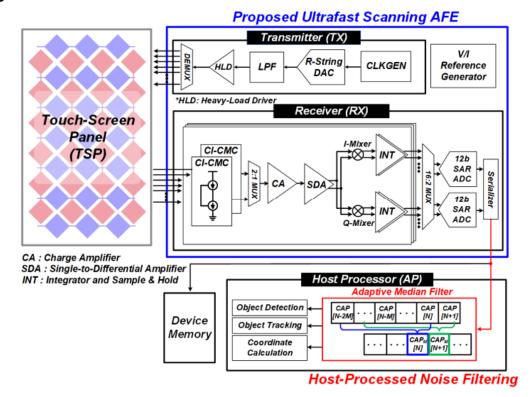

[그림 3] 제안하는 touch sensor 구조

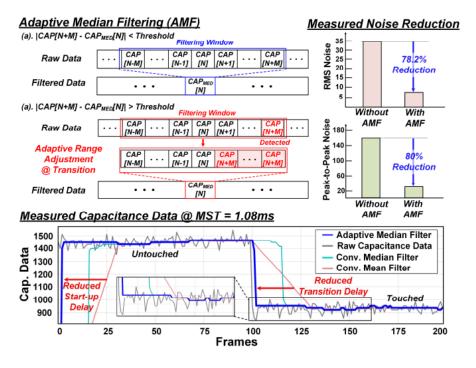

7-3번 논문은, 빠른 refresh rate을 요구하는 touch sensor에서 쓰일 수 있는 구조를 제안하였다. 제안하는 touch sensor은 이전에 사용되었던 analog domain의 noise filtering 등의 기법을 사용하는 대신, adaptive median filter을 사용하여 post-processing으로 noise 를 filtering하고, 이로 인해 시간을 소모하는 analog noise filtering 없이 빠른 속도로 출력을 얻어내면서 높은 SNR을 얻을 수 있다. 또한, 빠른 동작을 위해 driving signal frequency를 500kHz로 높이면서 높은 driving frequency로 인한 Rx phase error을 제거하기 위해 I/Q modulation을 사용하였다. 마지막으로, charge-interpolated common-mode compensator (CI-CMC)를 사용하여 differential sensing 보다 더 효과적으로 common noise를 제거한다.

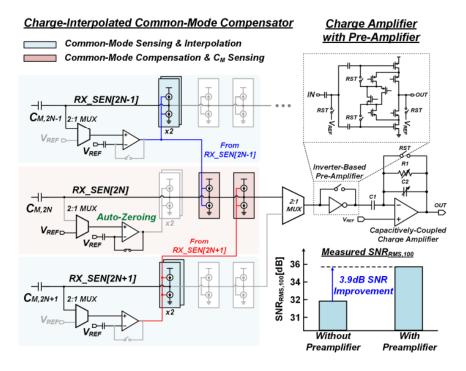

[그림 4]는 논문에서 제안하는 CI-CMC를 설명한다. 이는 이전의 differential sensing과

다르게, sensing하는 channel의 noise를 옆에 있는 channel에서 빼 주는 것이 아니라, 양 옆의 channel에서 가져와서 이를 averaging 하여 빼 주는 형태를 취한다. 다만, 이러한 방식의 common noise 제거는 differential 방식과 크게 다르다고 할 수 없고, 바로 옆 채널 대신 양 옆 채널의 common noise를 가져와 빼는 점만 다르다.

[그림 4] 제안하는 CI-CMC

[그림 5]는 제안하는 adaptive median filter (AMF)를 보여준다. 이는 이전의 mean filter 및 median filter와 비슷하게 moving average filter 형태를 취하지만, data에 큰 transition 이 일어날 때 transition 구간을 감지하여 mean을 취할 구간을 빠르게 다시 설정해 출력 data의 변화가 빠르게 일어나도록 하는 것이 장점이다.

[그림 5] 제안하는 AMF

### 저자정보

## 명예기자 임규완

● 소 속: KAIST 전기및전자공학과 박사과정

● 연구분야: Display Driver IC, Readout IC

● 이 메 일 : limkw@kaist.ac.kr

● 홈페이지: https://ICdesignlab.net